# FRONTGRADE DATASHEET UT54ACS244E

Octal Buffers & Line Drivers

3/16/2015 Version #: 1.0.0

#### **Features**

- Three-state outputs drive bus lines or buffer memory address registers

- 0.6µm CRH CMOS Process

- > Latchup immune

- · High speed

- · Low power consumption

- Wide power supply operating range of 3.0V to 5.5V

- Available QML Q or V processes

- · 20-lead flatpack

- UT54ACS244E SMD 5962-96570

# **Description**

The UT54ACS244E is a performance and voltage enhanced version of the UT54ACS244 non-inverting octal buffers and line drivers which improve the performance and density of three-state memory address drivers, clock drivers, and bus-oriented receivers and transmitters.

The devices are characterized over full military temperature range of -55°C to +125°C.

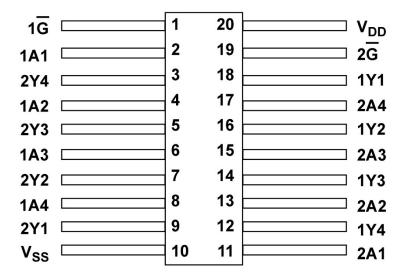

#### **Pinout**

Figure 1: 20-Lead Flatpack, Top View

## **Function Table**

| Inputs  |  | ıts | Output |

|---------|--|-----|--------|

| 1G , 2G |  | Α   | Υ      |

| L       |  | L   | L      |

| L       |  | Н   | н      |

| Н       |  | Х   | Z      |

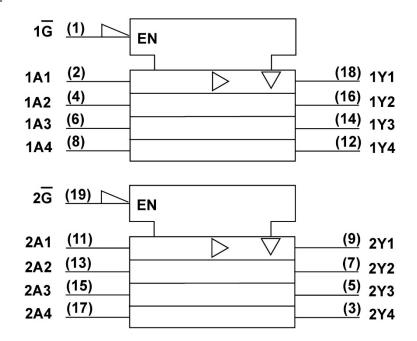

# **Logic Symbol**

#### Note

1. Logic symbol in accordance with ANSI/IEEE standard 91-1984 and IEC Publication 617-12.

3/16/2015 Version #: 1.0.0

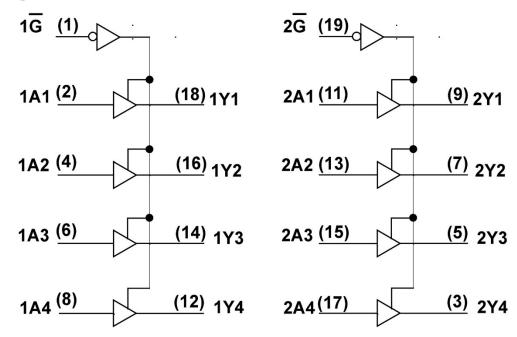

## **Logic Diagram**

# Operational Environment<sup>1</sup>

| Parameter                  | Limit  | Units      |

|----------------------------|--------|------------|

| Total Dose                 | 1.0E6  | rads(Si)   |

| SEU Threshold <sup>2</sup> | 108    | MeV-cm²/mg |

| SEL Threshold              | 120    | MeV-cm²/mg |

| Neutron Fluence            | 1.0E14 | n/cm²      |

#### Notes:

- 1. Logic will not latchup during radiation exposure within the limits defined in the table.

- 2. Device storage elements are immune to SEU affects.

## **Absolute Maximum Ratings**

| Symbol                      | Parameter                                                           | Limit                        | Units |

|-----------------------------|---------------------------------------------------------------------|------------------------------|-------|

| V <sub>DD</sub>             | Supply voltage                                                      | -0.3 to 7.0                  | V     |

| V <sub>I/O</sub>            | Voltage any pin                                                     | -0.3 to V <sub>DD</sub> +0.3 | V     |

| T <sub>STG</sub>            | Storage Temperature range                                           | -65 to +150                  | °C    |

| Tı                          | Maximum junction temperature                                        | +175                         | °C    |

| T <sub>LS</sub>             | Lead temperature (soldering 5 seconds)                              | +300                         | °C    |

| <del>O</del> JC             | Thermal resistance junction to case                                 | 15                           | °C/W  |

| I <sub>I</sub>              | DC input current                                                    | ±10                          | mA    |

| P <sub>D</sub> <sup>2</sup> | Maximum package power dissipation permitted @ $T_C = +125^{\circ}C$ | 3.2                          | W     |

#### Notes:

- 1. Stresses outside the listed absolute maximum ratings may cause permanent damage to the device. This is a stress rating only, functional operation of the device at these or any other conditions beyond limits indicated in the operational sections is not recommended. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

- 2. Per MIL-STD-883, method 1012.1, Section 3.4.1,  $P_D = (T_{j(max)} T_{C(max)}) / \Theta_{JC}$

# **Recommended Operating Conditions**

| Symbol          | Parameter             | Limit                | Units |

|-----------------|-----------------------|----------------------|-------|

| $V_{DD}$        | Supply voltage        | 3.0 to 5.5           | V     |

| V <sub>IN</sub> | Input voltage any pin | 0 to V <sub>DD</sub> | V     |

| T <sub>C</sub>  | Temperature range     | -55 to + 125         | °C    |

## **Electrical Characteristics for the UT54ACS244E**<sup>7</sup>

$(V_{DD} = 3.0V \text{ to } 5.5V; V_{SS} = 0V^6; -55^{\circ}C < T_C < +125^{\circ}C);$

| Symbol              | Description                                 | Condition                                                                              | MIN                 | MAX                | Unit   |

|---------------------|---------------------------------------------|----------------------------------------------------------------------------------------|---------------------|--------------------|--------|

| V <sub>IL</sub>     | Low-level input voltage <sup>1</sup>        | V <sub>DD</sub> = 3.0V to 5.5V                                                         |                     | 0.3V <sub>DD</sub> | V      |

| $V_{IH}$            | High-level input voltage <sup>1</sup>       | V <sub>DD</sub> = 3.0V to 5.5V                                                         | 0.7V <sub>DD</sub>  |                    | V      |

| I <sub>IN</sub>     | Input leakage current                       | $V_{IN} = V_{DD}$ or $V_{SS}$                                                          | -1                  | 1                  | μΑ     |

| V <sub>OL</sub>     | Low-level output voltage <sup>3</sup>       | I <sub>OL</sub> = 100μA<br>V <sub>DD</sub> = 3.0V to 5.5V                              |                     | 0.25               | V      |

| V <sub>OH</sub>     | High-level output voltage <sup>3</sup>      | $I_{OH} = -100 \mu A$<br>$V_{DD} = 3.0 V \text{ to } 5.5 V$                            | V <sub>DD</sub> 025 |                    | V      |

| I <sub>OS1</sub>    | Short-circuit output current <sup>2,4</sup> | $V_O = V_{DD}$ and $V_{SS}$<br>$V_{DD}$ from 4.5V to 5.5V                              | -300                | +300               | mA     |

| I <sub>OS2</sub>    | Short-circuit output current <sup>2,4</sup> | $V_O = V_{DD}$ and $V_{SS}$<br>$V_{DD}$ from 3.0V to 3.6V                              | -150                | +150               | mA     |

| I <sub>OL1</sub>    | Low level output current <sup>10</sup>      | $V_{IN} = V_{DD}$ or $V_{SS}$<br>$V_{OL} = 0.4V$<br>$V_{DD}$ from 4.5V to 5.5V         | +12                 |                    | mA     |

| I <sub>OL2</sub>    | Low level output current <sup>10</sup>      | $V_{IN} = V_{DD}$ or $V_{SS}$<br>$V_{OL} = 0.4V$<br>$V_{DD}$ from 3.0V to 3.6V         | +8                  |                    | mA     |

| I <sub>OH1</sub>    | High level output current <sup>10</sup>     | $V_{IN} = V_{DD}$ or $V_{SS}$<br>$V_{OH} = V_{DD}$ -0.4V<br>$V_{DD}$ from 4.5V to 5.5V | -12                 |                    | mA     |

| I <sub>OH2</sub>    | High level output current <sup>10</sup>     | $V_{IN} = V_{DD}$ or $V_{SS}$<br>$V_{OH} = V_{DD}$ -0.4V<br>$V_{DD}$ from 3.0V to 3.6V | -8                  |                    | mA     |

| I <sub>OZ</sub>     | Three-state output leakage current          | $V_O = V_{DD}$ and $V_{SS}$                                                            | -30                 | 30                 | μΑ     |

| P <sub>total1</sub> | Power dissipation <sup>2, 8, 9</sup>        | C <sub>L</sub> = 50pF<br>V <sub>DD</sub> from 4.5V to 5.5V                             |                     | 1.5                | mW/MHz |

| P <sub>total2</sub> | Power dissipation <sup>2, 8, 9</sup>        | C <sub>L</sub> = 50pF<br>V <sub>DD</sub> from 3.0V to 3.6V                             |                     | 0.75               | mW/MHz |

| I <sub>DDQ</sub>    | Quiescent Supply Current                    | $V_{IN} = V_{DD}$ or $V_{SS}$<br>$V_{DD}$ from 3.6V to 5.5V                            |                     | 25                 | μΑ     |

| C <sub>IN</sub>     | Input capacitance <sup>5</sup>              | f = 1MHz<br>$V_{DD} = 0V$                                                              |                     | 15                 | pF     |

| Соит                | Output capacitance <sup>5</sup>             | f = 1MHz<br>$V_{DD} = 0V$                                                              |                     | 15                 | pF     |

#### Notes:

- 1. Functional tests are conducted in accordance with MIL-STD-883 with the following input test conditions:  $V_{IH} = V_{IH}(min) + 20\%$ , -0%;  $V_{IL} = V_{IL}(max) + 0\%$ , -50%, as specified herein, for TTL, CMOS, or Schmitt compatible inputs. Devices may be tested using any input voltage within the above specified range, but are guaranteed to  $V_{IH}(min)$  and  $V_{IL}(max)$ .

- 2. Supplied as a design limit but not guaranteed or tested.

- 3. Per MIL-PRF-38535, for current density ≤5.0E5 amps/cm², the maximum product of load capacitance (per output buffer) times frequency should not exceed 3,765pF/MHz.

- 4. Not more than one output may be shorted at a time for maximum duration of one second.

- 5. Capacitance measured for initial qualification and when design changes may affect the value. Capacitance is measured between the designated terminal and V<sub>SS</sub> at frequency of 1MHz and a signal amplitude of 50mV rms maximum.

- 6. Maximum allowable relative shift equals 50mV.

- 7. For devices procured with a total ionizing dose tolerance guarantee, the post-irradiation performance is guaranteed at 25°C per MIL-STD-883 method 1019 condition A up to the maximum TID level procured.

- 8. Power does not include power contribution of any TTL output sink current.

- 9. Power dissipation specified per switching output.

- 10. Guaranteed by characterization, but not tested.

### AC Electrical Characteristics for the UT54ACS244E<sup>2</sup>

$(V_{DD} = 3.0V \text{ to } 5.5V; V_{SS} = 0V^1, -55^{\circ}C < T_C < +125^{\circ}C);$

| Symbol           | Parameter                | Condition             | VDD          | Minimum | Maximum | Unit |

|------------------|--------------------------|-----------------------|--------------|---------|---------|------|

| _                | Innut to Va              | C 50=5                | 4.5V to 5.5V | 1       | 6.5     |      |

| t <sub>PLH</sub> | Input to Yn              | C <sub>L</sub> = 50pF | 3.0V to 3.6V | 1       | 9.5     | ns   |

|                  | Innut to Va              | C 50=5                | 4.5V to 5.5V | 1       | 7.5     |      |

| t <sub>PHL</sub> | Input to Yn              | C <sub>L</sub> = 50pF | 3.0V to 3.6V | 1       | 10.5    | ns   |

| _                | G low to Yn active       | C <sub>L</sub> = 50pF | 4.5V to 5.5V | 1       | 6       | ns   |

| t <sub>PZL</sub> | G low to Yn active       |                       | 3.0V to 3.6V | 1       | 8       |      |

| _                | G low to Yn active       | C = F0mF              | 4.5V to 5.5V | 1       | 7       | ns   |

| t <sub>PZH</sub> | G low to Yn active       | C <sub>L</sub> = 50pF | 3.0V to 3.6V | 1       | 9.5     |      |

| _                | C high to Vn three state | C                     | 4.5V to 5.5V | 1       | 6       | nc   |

| t <sub>PLZ</sub> | G high to Yn three-state | C <sub>L</sub> = 50pF | 3.0V to 3.6V | 1       | 7.5     | ns   |

|                  | C high to Vo three state | C <sub>L</sub> = 50pF | 4.5V to 5.5V | 1       | 9.5     | nc   |

| t <sub>PHZ</sub> | G high to Yn three-state |                       | 3.0V to 3.6V | 1       | 11      | ns   |

#### Notes

- 1. Maximum allowable relative shift equals 50mV.

- 2. For devices procured with a total ionizing dose tolerance guarantee, the post-irradiation performance is guaranteed at 25°C per MIL-STD-883 method 1019 condition A up to the maximum TID level procured.

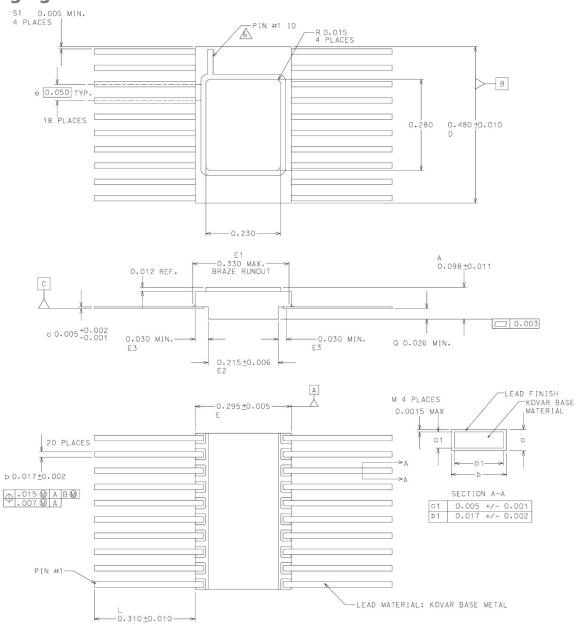

## **Packaging**

Figure 2: 20-lead Flatpack

#### Notes:

- 1. All exposed metallized areas are gold plated over electroplated nickel per MIL-PRF-38535.

- 2. The lid is electrically connected to  $V_{SS}$ .

- 3. Lead finishes are in accordance with MIL-PRF-38535.

- 4. Dimension symbol is in accordance with MIL-PRF-38533.

- 5. Lead position and colanarity are not measured.

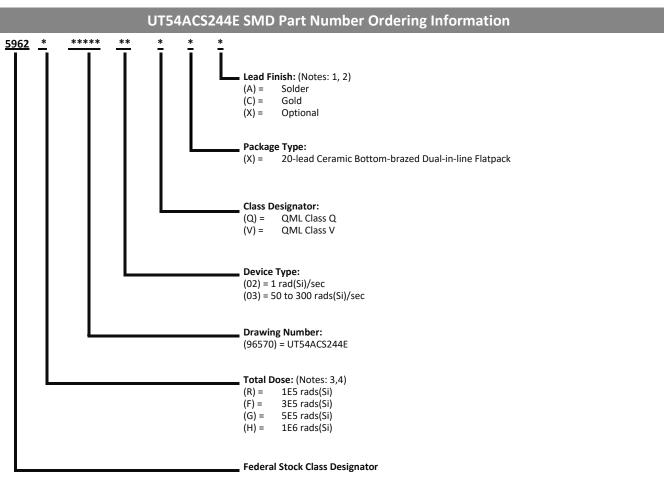

# **Ordering Information**

#### Notes:

- 1. Lead finish (A, C or X) must be specified.

- 2. If an "X" is specified when ordering, part marking will match the lead finish and will be either "A" (solder) or "C" (gold).

- 3. Total dose radiation must be specified when ordering. QML Q and QML V not available without radiation hardening. For prototype inquiries, contact factory.

- 4. Device type 02 is only offered with a TID tolerance guarantee of 3E5 rads(Si) or 1E6 rads(Si) and is tested in accordance with MIL-STD-883 Test Method 1019 Condition A and section 3.11.2. Device type 03 is only offered with a TID tolerance guarantee of 1E5 rads(Si), 3E5 rads(Si), and 5E5 rads(Si), and is tested in accordance with MIL-STD-883 Test Method 1019 Condition A.

## **Revision History**

| Date | Revision # | Author | Change Description           | Page # |

|------|------------|--------|------------------------------|--------|

| 3/15 | 1.0.0      |        | Initial Release of Datasheet |        |

|      |            |        |                              |        |

|      |            |        |                              |        |

|      |            |        |                              |        |

## **Datasheet Definitions**

|                       | Definition                                                                                                                                                                                                                                                                                                    |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Advanced Datasheet    | Frontgrade reserves the right to make changes to any products and services described herein at any time without notice. The product is still in the development stage and the <b>datasheet is subject to change</b> . Specifications can be <b>TBD</b> and the part package and pinout are <b>not final</b> . |

| Preliminary Datasheet | Frontgrade reserves the right to make changes to any products and services described herein at any time without notice. The product is in the characterization stage and prototypes are available.                                                                                                            |

| Datasheet             | Product is in production and any changes to the product and services described herein will follow a formal customer notification process for form, fit or function changes.                                                                                                                                   |

Frontgrade Technologies Proprietary Information Frontgrade Technologies (Frontgrade or Company) reserves the right to make changes to any products and services described herein at any time without notice. Consult a Frontgrade sales representative to verify that the information contained herein is current before using the product described herein. Frontgrade does not assume any responsibility or liability arising out of the application or use of any product or service described herein, except as expressly agreed to in writing by the Company; nor does the purchase, lease, or use of a product or service convey a license to any patents rights, copyrights, trademark rights, or any other intellectual property rights of the Company or any third party.