# FRONT GRADE DATASHEET

UT32BS1X833 Matrix-D™

32-Channel 1:8 Bus Switch

11/6/2023

Version: 2.0.0

## **Features**

- Interfaces to standard processor memory busses

- Single-chip interface that provides memory paging to industry- standard SDRAMS

- · Eliminates need for additional logic or FPGA

- I/O channels functional to 3.3V

- RON 5 Ohms typical

- Flat RON characteristics over channel voltage

- · Propagation delay 204ps through switch

- Transmission gate technology allows for true bi-directional operation

- Internal pull-up resistors on the first 8 outputs of each bank to ensure memory devices remain in off state when channels de-selected

- Bus holders maintain output states on all other outputs when channels de-selected

- Logic power 1mW/MHz

- Temperature range -55°C to 125°C

- Operational environment:

- Intrinsic total-dose: up to 300 krad(Si)

- SEL Immune ≤100 MeV-cm<sup>2</sup>/mg

- · Packaging options:

- 400-pin Ceramic Land Grid, Column Grid and Ball Grid Array packages; 1mm pitch

- Standard Microcircuit Drawing 5962-15243

- · QML Q and V

# **Applications**

- · Microprocessor interfaces that require large amounts of SDRAM memory

- High-speed applications or systems with large bus capacitance

- · Cost-sensitive applications that require bus isolation without an expensive FPGA

- · Large SDRAM paging architecture

## Introduction

The UT32BS1X833 Matrix-D™ is a 32-Channel, 1:8 Bus Switch, that provides bus isolation for up to eight banks of 32 I/O connections. By providing bus isolation, the UT32BS1X833 can significantly reduce the amount of load capacitance seen by a host processor and memory devices. The enable to output delay time is only 4.1ns (typical). The reduction in both load capacitance and delay time significantly increase speed and performance compared with a discrete logic or FPGA memory interface solution.

The UT32BS1X833 operates from a single 3.3V supply. The bus channels can pass any voltage between  $V_{SS}$  and  $V_{DD}$ , allowing the switching of signals using other standards, such as LVCMOS 1.8V. The input and output banks connect via analog channels that have an RON that is nominally 5 Ohms over the entire input voltage range. The flat RON eliminates the need to add external series resistors for source impedance termination.

The UT32BS1X833 has a "broadcast mode" that is enabled by driving both  $\overline{SDCS[1]}$  and  $\overline{SDCS[0]}$  low. In this mode, all banks are active, which facilitates SDRAM refresh and initialization cycles.

Each UT32BS1X833 can interface up to eight of the Frontgrade 2.5Gb or 3.0Gb SDRAM MCM devices with any Frontgrade LEON processor without the need for additional logic.

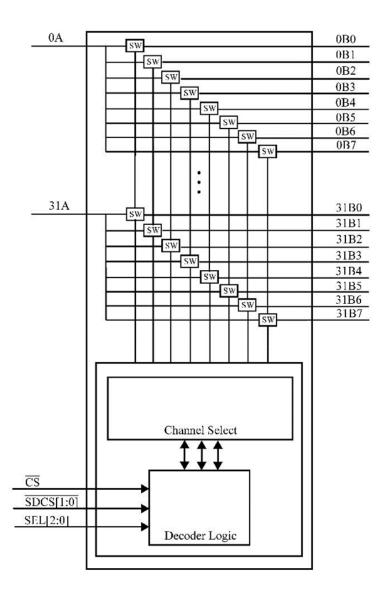

The UT32BS1X833 32-Channel 1:8 Bus Switch is built on the Frontgrade  $0.35\mu m$  process. The device incorporates control logic that electrically connects input bank A to the output banks B0-B7, depending upon the selected channel. Figure 1 shows a block diagram of the device. Figure 1 shows a block diagram of the device. The  $\overline{CS}$  input is a master device select input that enables the device when asserted low. When high, the device is in active, and all outputs are turned off, except in the case of a refresh or initialization cycle. Refresh and initialization cycles are automatically passed on to all connected SDRAM devices when  $\overline{SDCS[1]}$  and  $\overline{SDCS[0]}$  are both asserted low. During either of these cycles, all output banks are turned on. The select inputs SEL[2:0] determine which bank is turned on for normal SDRAM read and write operations.

Figure 1. UT32BS1X833 Functional Block Diagram

## **Functional Tables**

## **Table 1. Truth Table for Digital Inputs and Channels**

|    | Inputs     |        |        |        | Selected Banks |   |   |   |   |   |   |   |

|----|------------|--------|--------|--------|----------------|---|---|---|---|---|---|---|

| CS | SDCS[1:0]  | SEL[2] | SEL[1] | SEL[0] | 7              | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| 1  | X1b or 1Xb | Х      | Х      | Х      |                |   |   |   |   |   |   |   |

| Х  | 00b        | Х      | Х      | Х      | •              | • | • | • | • | • | • | • |

| 0  | X1b or 1Xb | 0      | 0      | 0      |                |   |   |   |   |   |   | • |

| 0  | X1b or 1Xb | 0      | 0      | 1      |                |   |   |   |   |   | • |   |

| 0  | X1b or 1Xb | 0      | 1      | 0      |                |   |   |   |   | • |   |   |

| 0  | X1b or 1Xb | 0      | 1      | 1      |                |   |   |   | • |   |   |   |

| 0  | X1b or 1Xb | 1      | 0      | 0      |                |   |   | • |   |   |   |   |

| 0  | X1b or 1Xb | 1      | 0      | 1      |                |   | • |   |   |   |   |   |

| 0  | X1b or 1Xb | 1      | 1      | 0      |                | • |   |   |   |   |   |   |

| 0  | X1b or 1Xb | 1      | 1      | 1      | •              |   |   |   |   |   |   |   |

The table above indicates which banks are active based upon the selected input logic. All banks are in a high-Z state when unselected.

# **Pin Identification and Description**

## **Logic Pins**

| Pin Name | Direction | Pin Number | Description                                                   |

|----------|-----------|------------|---------------------------------------------------------------|

| CS       | I         | M11        | Master chip select for device                                 |

| SDCS[0]  | ı         | M10        | Enables broadcast mode when 00b. Otherwise, normal operation. |

| SDCS[1]  | ı         | N10        | Enables broadcast mode when 00b. Otherwise, normal operation. |

| SEL[0]   | I         | P9         | Bit 0 of bank select logic.                                   |

| SEL[1]   | ı         | P10        | Bit 1 of bank select logic.                                   |

| SEL[2]   | ı         | R10        | Bit 2 of bank select logic.                                   |

## **Channel Pins**

| Pin<br>Name | Pin<br>Number |

|-------------|---------------|-------------|---------------|-------------|---------------|-------------|---------------|-------------|---------------|

| 0A          | T4            | 0В0         | R3            | 0B1         | U4            | 0B2         | U3            | 0B3         | Т3            |

| 1A          | M3            | 1B0         | R1            | 1B1         | Р3            | 1B2         | N3            | 1B3         | P2            |

| 2A          | L1            | 2B0         | U2            | 2B1         | V1            | 2B2         | L2            | 2B3         | M2            |

| 3A          | M4            | 3B0         | N6            | 3B1         | N5            | 3B2         | N8            | 3B3         | M5            |

| 4A          | M8            | 4B0         | P5            | 4B1         | R4            | 4B2         | N4            | 4B3         | P4            |

| Pin  | Pin    |

|------|--------|------|--------|------|--------|------|--------|------|--------|

| Name | Number |

| 5A   | К9     | 5B0  | L10    | 5B1  | L8     | 5B2  | L9     | 5B3  | K8     |

| 6A   | G5     | 6B0  | G4     | 6B1  | F5     | 6B2  | H4     | 6B3  | F6     |

| 7A   | H7     | 7B0  | J4     | 7B1  | H5     | 7B2  | J6     | 7B3  | Н6     |

| 8A   | D2     | 8B0  | K1     | 8B1  | К2     | 8B2  | C1     | 8B3  | D1     |

| 9A   | E1     | 9B0  | Н3     | 9B1  | G2     | 9B2  | G3     | 9B3  | G1     |

| 10A  | D5     | 10B0 | C6     | 10B1 | D4     | 10B2 | C4     | 10B3 | C5     |

| 11A  | C9     | 11B0 | A6     | 11B1 | C7     | 11B2 | C8     | 11B3 | В7     |

| 12A  | A10    | 12B0 | B4     | 12B1 | A3     | 12B2 | B10    | 12B3 | В9     |

| 13A  | D9     | 13B0 | F8     | 13B1 | E8     | 13B2 | F9     | 13B3 | E9     |

| 14A  | Н9     | 14B0 | E7     | 14B1 | D6     | 14B2 | D8     | 14B3 | D7     |

| 15A  | H11    | 15B0 | J10    | 15B1 | K11    | 15B2 | H10    | 15B3 | J11    |

| 16A  | D15    | 16B0 | F12    | 16B1 | D13    | 16B2 | D14    | 16B3 | E14    |

| 17A  | E13    | 17B0 | E12    | 17B1 | D12    | 17B2 | H13    | 17B3 | F13    |

| 18A  | A17    | 18B0 | B12    | 18B1 | A11    | 18B2 | B11    | 18B3 | A18    |

| 19A  | A15    | 19B0 | B13    | 19B1 | C13    | 19B2 | B14    | 19B3 | C14    |

| 20A  | E18    | 20B0 | D18    | 20B1 | F18    | 20B2 | F17    | 20B3 | E17    |

| 21A  | H19    | 21B0 | G20    | 21B1 | G18    | 21B2 | G19    | 21B3 | H18    |

| 22A  | J19    | 22B0 | D20    | 22B1 | C20    | 22B2 | K19    | 22B3 | K20    |

| 23A  | J16    | 23B0 | H15    | 23B1 | J15    | 23B2 | H16    | 23B3 | J17    |

| 24A  | K14    | 24B0 | J12    | 24B1 | K15    | 24B2 | J13    | 24B3 | J14    |

| 25A  | M15    | 25B0 | L11    | 25B1 | L15    | 25B2 | L14    | 25B3 | M14    |

| 26A  | L16    | 26B0 | P16    | 26B1 | R16    | 26B2 | L18    | 26B3 | L17    |

| 27A  | M20    | 27B0 | N15    | 27B1 | P15    | 27B2 | N14    | 27B3 | N20    |

| 28A  | N19    | 28B0 | U19    | 28B1 | U20    | 28B2 | V19    | 28B3 | W19    |

| 29A  | T19    | 29B0 | R20    | 29B1 | P20    | 29B2 | T20    | 29B3 | R19    |

| 30A  | V16    | 30B0 | V17    | 30B1 | V15    | 30B2 | U15    | 30B3 | U16    |

| 31A  | W13    | 31B0 | Y15    | 31B1 | V14    | 31B2 | W14    | 31B3 | V13    |

| 0B4  | T2     | 0B5  | R2     | 0B6  | T1     | 0B7  | P1     |      |        |

| 1B4  | N2     | 1B5  | W2     | 1B6  | V2     | 1B7  | U1     |      |        |

| 2B4  | M1     | 2B5  | N1     | 2B6  | N7     | 2B7  | P6     |      |        |

| 3B4  | L5     | 3B5  | L4     | 3B6  | L3     | 3B7  | R5     |      |        |

| 4B4  | M6     | 4B5  | M7     | 4B6  | L7     | 4B7  | L6     |      |        |

| 5B4  | K7     | 5B5  | J7     | 5B6  | J8     | 5B7  | К6     |      |        |

| Pin  | Pin    |

|------|--------|------|--------|------|--------|------|--------|------|--------|

| Name | Number |

| 6B4  | K4     | 6B5  | К3     | 6B6  | K5     | 6B7  | J5     |      |        |

| 7B4  | G6     | 7B5  | J1     | 7B6  | H1     | 7B7  | J2     |      |        |

| 8B4  | C3     | 8B5  | C2     | 8B6  | J3     | 8B7  | H2     |      |        |

| 9B4  | F1     | 9B5  | E2     | 9B6  | F2     | 9B7  | E3     |      |        |

| 10B4 | B5     | 10B5 | В6     | 10B6 | A5     | 10B7 | A7     |      |        |

| 11B4 | B8     | 11B5 | B2     | 11B6 | В3     | 11B7 | A4     |      |        |

| 12B4 | A9     | 12B5 | A8     | 12B6 | G8     | 12B7 | F7     |      |        |

| 13B4 | E10    | 13B5 | D10    | 13B6 | C10    | 13B7 | E6     |      |        |

| 14B4 | Н8     | 14B5 | G9     | 14B6 | G10    | 14B7 | F10    |      |        |

| 15B4 | F11    | 15B5 | G12    | 15B6 | G11    | 15B7 | H12    |      |        |

| 16B4 | E15    | 16B5 | D11    | 16B6 | C11    | 16B7 | E11    |      |        |

| 17B4 | G13    | 17B5 | F14    | 17B6 | A12    | 17B7 | A13    |      |        |

| 18B4 | B17    | 18B5 | B19    | 18B6 | B18    | 18B7 | C12    |      |        |

| 19B4 | A16    | 19B5 | A14    | 19B6 | B16    | 19B7 | B15    |      |        |

| 20B4 | F19    | 20B5 | E19    | 20B6 | F20    | 20B7 | E20    |      |        |

| 21B4 | J18    | 21B5 | C19    | 21B6 | C18    | 21B7 | D19    |      |        |

| 22B4 | H20    | 22B5 | J20    | 22B6 | G15    | 22B7 | H14    |      |        |

| 23B4 | K16    | 23B5 | K18    | 23B6 | K17    | 23B7 | G16    |      |        |

| 24B4 | K12    | 24B5 | K13    | 24B6 | L12    | 24B7 | L13    |      |        |

| 25B4 | M13    | 25B5 | P17    | 25B6 | N17    | 25B7 | R17    |      |        |

| 26B4 | M17    | 26B5 | M16    | 26B6 | N13    | 26B7 | N16    |      |        |

| 27B4 | L20    | 27B5 | M19    | 27B6 | L19    | 27B7 | V20    |      |        |

| 28B4 | M18    | 28B5 | P19    | 28B6 | N18    | 28B7 | P18    |      |        |

| 29B4 | T17    | 29B5 | T18    | 29B6 | U18    | 29B7 | U17    |      |        |

| 30B4 | W15    | 30B5 | W16    | 30B6 | Y14    | 30B7 | Y16    |      |        |

| 31B4 | V12    | 31B5 | W18    | 31B6 | V18    | 31B7 | W17    |      |        |

## **Power and Ground Pins**

| Pin Name        | Pin Number                                                                                                                                                                                                                                                                                                                                                                       | Description   |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| V <sub>DD</sub> | A2, A20, B1, E5, G14, P7, T16, W20, Y1, Y19                                                                                                                                                                                                                                                                                                                                      | Power Supply  |

| V <sub>SS</sub> | A1, A19, B20, E16, G7, P14, T5, U5, W01, Y02, Y20                                                                                                                                                                                                                                                                                                                                | Ground        |

| Test Mode       | R15                                                                                                                                                                                                                                                                                                                                                                              |               |

| NC              | K10, V4,                                                                                                                                                                                                                                                                                                                                                                         | No Connect    |

| Spare[0:81]     | J9, E4, F4, F3, D3, C16, D16, D17, C15, C17, F15, H17, F16, G17, R18, Y17, Y18, W11, Y11, W12, Y13, Y12, R14, P13, T13, R13, R12, U12, T12, T11, V11, U11, U14, T15, T14, P12, U13, N12, P11, N11, M12, R11, M9, N9, U7, U8, U6, T7, T6, V10, U10, T10, U9, T9, R9, T8, R8, R7, P8, Y8, Y9, Y10, W9, W10, V3, W4, Y4, W3, Y3, W8, V9, W7, V8, V7, Y6, Y7, Y5, W6, W5, V5, R6, V6 | Tie to ground |

# **Absolute Maximum Ratings**

## (Referenced to Vss) 1

| Symbol           | Parameters                                                 | Value                                        | Units |

|------------------|------------------------------------------------------------|----------------------------------------------|-------|

| V <sub>DD</sub>  | Supply voltage <sup>2</sup>                                | -0.3 to 4.8                                  | V     |

| V <sub>IO</sub>  | Input voltage any pin <sup>2</sup>                         | V <sub>SS</sub> -0.3 to V <sub>DD</sub> +0.3 | V     |

| V <sub>CH</sub>  | Input voltage any bussed pin <sup>2</sup>                  | V <sub>SS</sub> -0.3 to V <sub>DD</sub> +0.3 | V     |

| I <sub>IO</sub>  | Maximum dc I/O current any logic pin                       | -10 to 10                                    | mA    |

| P <sub>D</sub>   | Maximum power dissipation permitted @ TC=125C <sup>3</sup> | 5                                            | W     |

| TJ               | Junction temperature                                       | 150                                          | °C    |

| $\Theta_{JC}$    | Thermal resistance, junction to case                       | 5                                            | °C/W  |

| T <sub>STG</sub> | Storage temperature                                        | -65 to 150                                   | °C    |

| ESD              | ESD protection (human body model) Class 2                  | 2000                                         | V     |

- 1. Permanent device damage may occur if absolute maximum ratings are exceeded. Functional operation should be restricted to recommended operating conditions. Exposure to absolute maximum rating conditions for extended periods may affect device reliability and performance.

- 2. All voltages are referenced to V<sub>SS</sub>

- 3. Power dissipation capability depends on package characteristics and use environment.

# **Recommended Operating Conditions**

## (Referenced to V<sub>SS</sub>)

| Symbol          | Description                          | Conditions                                         | MIN | MAX             | Units |

|-----------------|--------------------------------------|----------------------------------------------------|-----|-----------------|-------|

| V <sub>DD</sub> | Supply voltage                       |                                                    | 3.0 | 3.6             | V     |

| V <sub>IN</sub> | Input voltage any pin                |                                                    | 0   | V <sub>DD</sub> | V     |

| T <sub>C</sub>  | Case operating temperature           |                                                    | -55 | 125             | °C    |

| t <sub>R</sub>  | Rise time, logic inputs              | Transition from V <sub>IL</sub> to V <sub>IH</sub> |     | 5               | ns    |

| t <sub>F</sub>  | Fall time, logic inputs              | Transition from V <sub>IH</sub> to V <sub>IL</sub> |     | 5               | ns    |

| I <sub>CH</sub> | Maximum DC I/O current any logic pin |                                                    | -60 | 60              | mA    |

## **Operational Environment**

| Operational Environment           |       |                         |

|-----------------------------------|-------|-------------------------|

| Parameter                         | Limit | Units                   |

| TID                               | 3.0E5 | Rad(Si)                 |

| Single Event Latchup Immune (SEL) | ≤100  | MeV-cm <sup>2</sup> /mg |

## Power Supply Operating Characteristics (Pre and Post-Radiation)\*

(V<sub>DD</sub> =  $3.3V \pm 0.3V$ ; V<sub>SS</sub>  $\leq$  VIN  $\leq$  V<sub>DD</sub>; - $55^{\circ}$ C < TC < 125 $^{\circ}$ C); Unless otherwise noted, TC is per the temperature range ordered

| Symbol           | Description            | Conditions                                                                                |                    | MIN | MAX    | Units |  |

|------------------|------------------------|-------------------------------------------------------------------------------------------|--------------------|-----|--------|-------|--|

| A <sub>IDD</sub> | Active supply current  | V <sub>DD</sub> =3.6V One SEL input toggling once                                         |                    | 1.5 | mA/MHz |       |  |

| Q <sub>IDD</sub> | Standby supply current |                                                                                           | -55°C and<br>+25°C |     | 20     | uA    |  |

|                  |                        | V <sub>DD</sub> =3.6V<br>CS=V <sub>DD</sub> , SDCS[1:0]=V <sub>DD</sub><br>Post Radiation | +125°C             |     | 20     |       |  |

|                  |                        |                                                                                           | +25°C              |     | 8000   | uA    |  |

<sup>\*</sup> For devices procured with a total ionizing dose tolerance guarantee, the post-irradiation performance is guaranteed at 25°C per MIL-STD-883 Method 1019, Condition A up to up to the maximum TID level procured.

# DC Characteristics for Logic Signals (Pre and Post-Radiation) \*

( $V_{DD}$  = 3.3V ± 0.3V;  $V_{SS} \le VIN \le V_{DD}$ ; -55°C < TC < 125°C); Unless otherwise noted, TC is per the temperature range ordered

| Symbol                        | Description              | Conditions                                   | MIN | MAX | Units |

|-------------------------------|--------------------------|----------------------------------------------|-----|-----|-------|

| V <sub>IH</sub>               | High-level input voltage | V <sub>DD</sub> = 3.6V                       | 2.0 |     | V     |

| V <sub>IL</sub>               | Low-level input voltage  | V <sub>DD</sub> =3.6V                        |     | 0.8 | V     |

|                               | land lank and a surrent  | VIN=V <sub>DD</sub> , V <sub>DD</sub> = 3.6V |     | 1   |       |

| I <sub>IN</sub>               | Input leakage current    | $VIN=V_{SS}$ , $V_{DD}=3.6V$                 | -1  |     | uA    |

| C <sub>IN</sub> <sup>1</sup>  | Input capacitance        | $V_{DD}$ =0 $V$<br>f=1MHz                    |     | 22  | pF    |

| C <sub>OUT</sub> <sup>1</sup> | Output capacitance       | $V_{DD}$ =0 $V$<br>f=1 $MHz$                 |     | 22  | pF    |

#### Notes:

- \* For devices procured with a total ionizing dose tolerance guarantee, the post-irradiation performance is guaranteed at 25°C per MIL-STD-883 Method 1019, Condition A up to the maximum TID level procured.

- 1. RL=50 $\Omega$ , CL=50 pF, VIN = 1V rms centered at  $V_{DD}/2$ .

- CIN and COUT shall be measured in accordance with MIL-STD-883, M3012 and only for the initial test and after

process or design changes which might affect capacitance. CIN shall be measured between the designated terminal or

V<sub>SS</sub> at a frequency of 1MHz. For CIN and COUT, test all pins on one device and then test four additional devices on

worst case pin for each I/O type.

# DC Characteristics for Bussed Signals (Pre and Post-Radiation) \*

$(V_{DD} = 3.3V \pm 0.3V; V_{SS} \le VIN \le V_{DD}; -55^{\circ}C < TC < 125^{\circ}C);$  Unless otherwise noted, TC is per the temperature range ordered

| Symbol                         | Description                          | Conditions                                                                                                        | MIN | MAX | Units |

|--------------------------------|--------------------------------------|-------------------------------------------------------------------------------------------------------------------|-----|-----|-------|

| C <sub>ON1</sub> <sup>4</sup>  | Switch ON capacitance                | Output is open $f=1$ MHz, $0.1$ V <sub>DD</sub> $\leq$ V <sub>i</sub> $\leq$ 0.9V <sub>DD</sub>                   |     | 17  | pF    |

| C <sub>ON2</sub> <sup>1</sup>  | Switch ON capacitance                | Broadcast mode, all outputs open $f=1$ MHz, $0.1$ V <sub>DD</sub> $\leq$ V <sub>i</sub> $\leq$ 0.9V <sub>DD</sub> |     | 50  | pF    |

| C <sub>OFF1</sub> <sup>4</sup> | Switch OFF capacitance at input mA   | Output is open f=1MHz                                                                                             |     | 11  | pF    |

| C <sub>OFF2</sub> <sup>4</sup> | Switch OFF capacitance at output mBn | $\begin{array}{c} \text{Input is open} \\ f = 1 \text{MHz} \end{array}$                                           |     | 5   | pF    |

| Symbol                             | Description                                                                                                                             | Conditions                                                                       | MIN        | MAX   | Units    |

|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|------------|-------|----------|

|                                    |                                                                                                                                         |                                                                                  |            |       |          |

| R <sub>ON</sub> <sup>2</sup>       | Switch ON resistance                                                                                                                    | $V_o$ = $V_{SS}$ , $V_{DD}$ , and $V_{DD}/2$ $I_{in}$ = $40$ mA                  |            | 12    | Ω        |

| R <sub>ON(flat)</sub> <sup>2</sup> | Switch ON resistance flatness                                                                                                           | $V_o$ = $V_{SS}$ , $V_{DD}$ , and $V_{DD}/2$ $I_{in}$ =-40mA                     |            | 5     | Ω        |

| I <sub>OFF</sub>                   | Switch OFF leakage current                                                                                                              | $V_i$ = $V_{SS}$ and $V_o$ = $V_{DD}$ , or $V_i$ = $V_{DD}$ and $V_o$ = $V_{SS}$ | -2         | 2     | uA       |

| I <sub>L</sub>                     | Leakage current for outputs<br>with pull-up resistors<br>(0B0-7B0, 0B1-7B1,<br>0B2-7B2, 0B3-7B3, 0B4-7B4,<br>0B5-7B5, 0B6-7B6, 0B7-7B7) | Output is off $V_o=V_{DD}$ $V_o=V_{SS}$                                          | -4<br>-100 | 4 -60 | uA<br>uA |

| I <sub>BHHL</sub> <sup>3</sup>     | Bus holder switch current<br>high to low<br>(8B0-31B0, 8B1-31B1,<br>8B2-31B2, 8B3-31B3,<br>8B4-31B4, 8B5-31B5,<br>8B6-31B6, 8B7-31B7)   | Output is off                                                                    | -500       | -150  | uA       |

| I <sub>BHLH</sub> <sup>3</sup>     | Bus holder switch current<br>low to high<br>(8B0-31B0, 8B1-31B1,<br>8B2-31B2, 8B3-31B3,<br>8B4-31B4, 8B5-31B5,<br>8B6-31B6, 8B7-31B7)   | Output is off                                                                    | 150        | 500   | uA       |

- \* For devices procured with a total ionizing dose tolerance guarantee, the post-irradiation performance is guaranteed at 25°C per MIL-STD-883 Method 1019, Condition A up toup to o the maximum TID level procured.

- 1. Guaranteed by design.

- 2. Guaranteed by device characterization.

- 3. Guaranteed by functional test only.

- 4. RL=50 $\Omega$ , CL=50 pF, VIN = 1V rms centered at  $V_{DD}/2$ .

- C<sub>ON1</sub>, C<sub>OFF1</sub> AND C<sub>OFF2</sub> shall be measured in accordance with MIL-STD-883, M3012 and only for the initial test and after process or design changes which might affect capacitance.

# AC Characteristics (Pre and Post-Radiation) \*

(V<sub>DD</sub> = 3.3V  $\pm$  0.3V; V<sub>SS</sub>  $\leq$  VIN  $\leq$  V<sub>DD</sub>; -55°C < TC < 125°C); Unless otherwise noted, TC is per the temperature range ordered

| Symbol                          | Description                      | Conditions                                                                                                                                                                                | MIN | MAX | Units |

|---------------------------------|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-------|

| t <sub>P,BUS</sub> <sup>1</sup> | Bussed signals propagation delay | From any $m$ A input to any $m$ B $n$ output                                                                                                                                              |     | 204 | ps    |

| t <sub>ON1</sub>                | Bussed signals ON time           | From $\overline{\text{CS}}$ or SEL to any $m\text{B}n$ output; $\overline{\text{SDCS}}$ static $\text{R}_{\text{L}}\text{=}50\Omega$ , $\text{C}_{\text{L}}\text{=}50\text{pF}$           | 1.7 | 7.5 | ns    |

| t <sub>OFF1</sub>               | Bussed signals OFF time          | From $\overline{\text{CS}}$ or SEL to any $m\text{B}n$ output; $\overline{\text{SDCS}}$ static $R_{\text{L}}$ =50 $\Omega$ , $C_{\text{L}}$ =50pF                                         | 1.7 | 7.5 | ns    |

| t <sub>ON2</sub> <sup>2</sup>   | Bussed signals ON time           | From $\overline{\rm SDCS}$ to any $m{\rm B}n$ output; $\overline{\rm CS}$ and SEL static R <sub>L</sub> =50 $\Omega$ , C <sub>L</sub> =50pF                                               | 1.7 | 8.0 | ns    |

| t <sub>OFF2</sub> <sup>2</sup>  | Bussed signals OFF time          | From $\overline{\text{SDCS}}$ to any $m\text{B}n$ output; $\overline{\text{CS}}$ and $\text{SEL}$ static $\text{R}_{\text{L}}\text{=}50\Omega$ , $\text{C}_{\text{L}}\text{=}50\text{pF}$ | 1.7 | 7.5 | ns    |

<sup>\*</sup> For devices procured with a total ionizing dose tolerance guarantee, the post-irradiation performance is guaranteed at 25°C per MIL-STD-883 Method 1019, Condition A up to the maximum TID level procured.

<sup>1.</sup> Not tested. The propagation delay through the channel is based upon the RC time constant of the maximum channel resistance and switch ON capacitance,  $12\Omega$  and 17pF.

<sup>2.</sup> Guaranteed by design

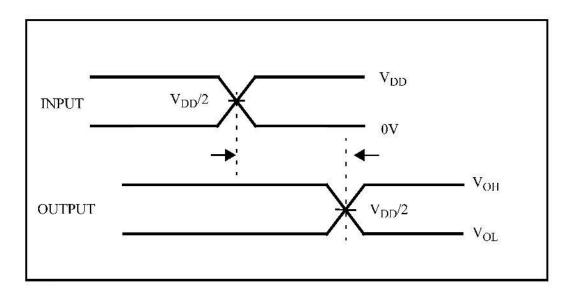

## **Parameter Measurement Information**

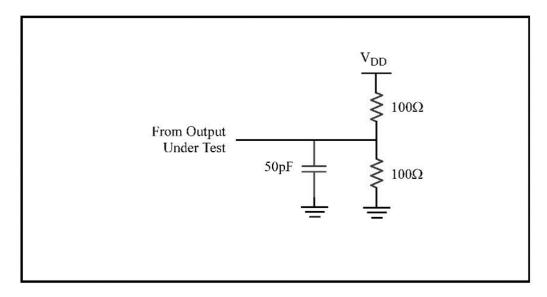

Figure 2: Load Circuit

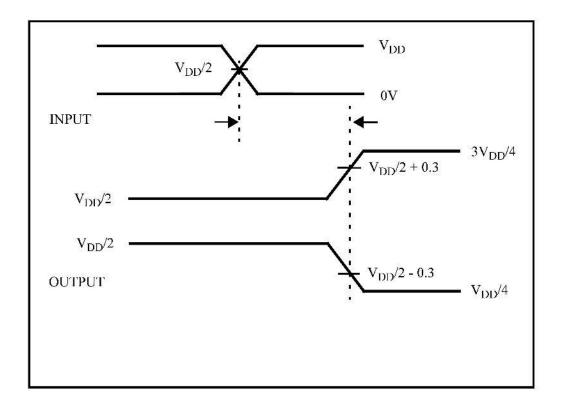

Figure 3: Bussed Signals Turn-on Time

#### Notes:

1. The bus input is driven to  $V_{DD}$  or  $V_{SS}$  through a  $50\Omega$  series resistor.

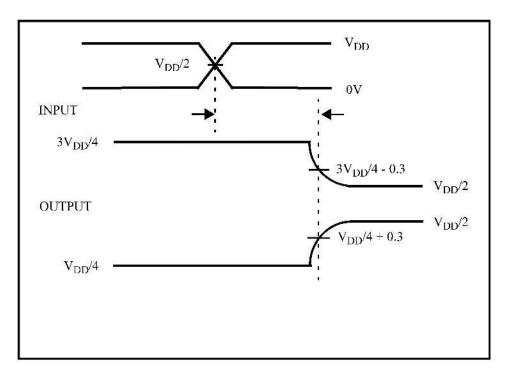

Figure 4: Bussed Signals Turn-off Time

#### Notes:

1. The bus input is driven to  $V_{DD}$  or  $V_{SS}$  through a  $50\Omega$  series resistor.

Figure 5: Logic and Buffered Output Delay

#### Notes:

1. The bus input is driven to  $V_{DD}$  or  $V_{SS}$  through a  $50\Omega$  series resistor.

## **Packaging**

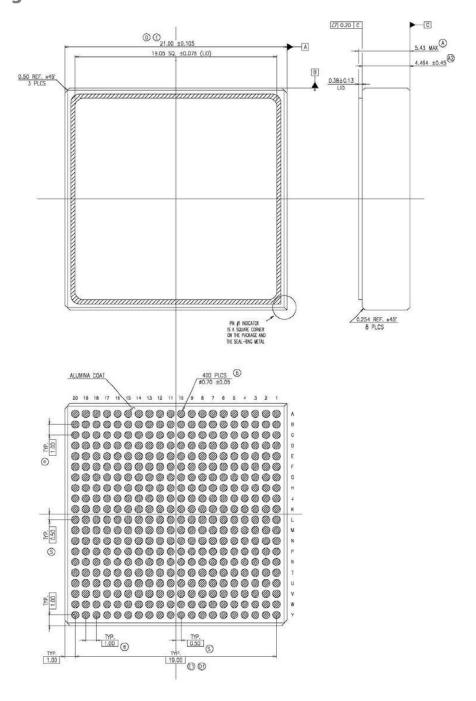

Figure 6: 400 pin Ceramic Land Grid Array Package (Case Outline Z)

- 1. Material Is 90% Alumina (ε<sub>r</sub>=9.8)

- 2. Lid is connected to  $V_{SS}$

- 3. Units are millimeters

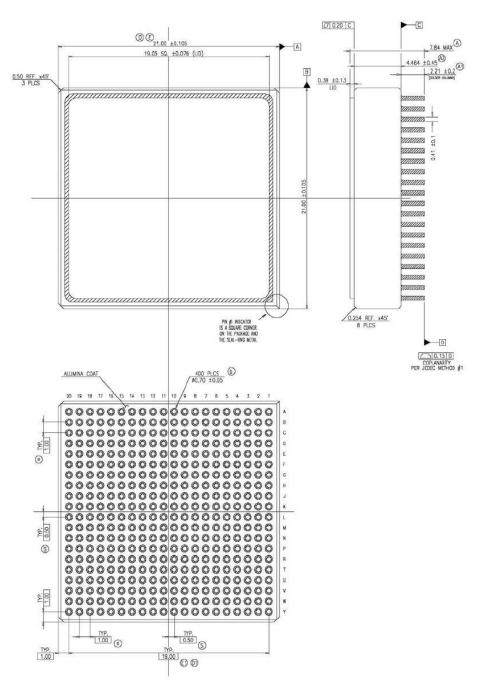

Figure 7: 400-pin Ceramic Column Grid Array Package (Case Outline S)

- 1. Material Is 90% Alumina ( $\epsilon_r$ =9.8)

- 2. Lid is connected to  $V_{SS}$

- 3. Units are millimeters

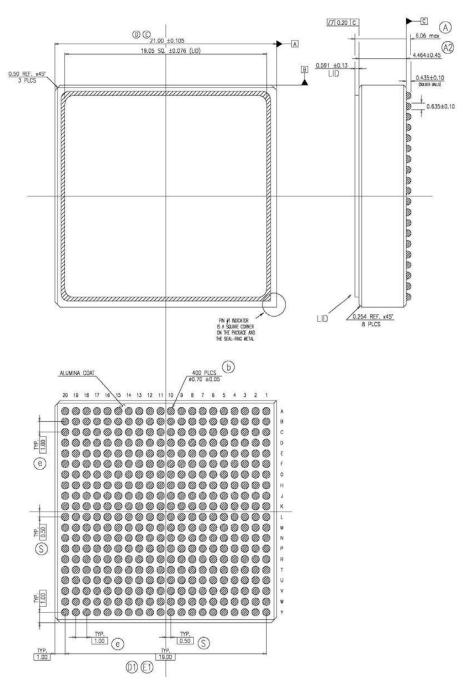

Figure 8: 400-pin Ceramic Ball Grid Array Package (Case Outline C)

- 1. Material is 90% Alumina ( $\epsilon_r$ =9.8)

- 2. Lid is connected to  $V_{SS}$

- 3. Units are millimeters

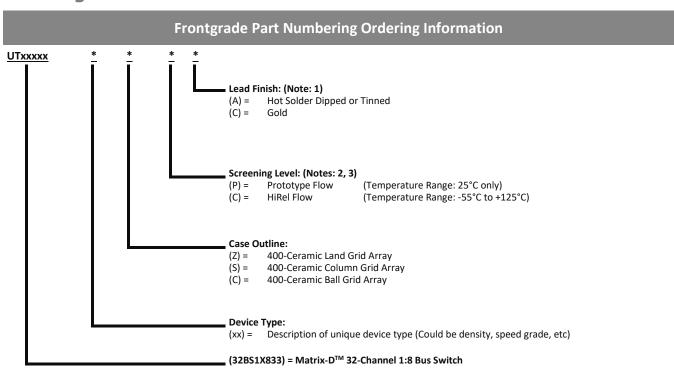

# **Ordering Information**

- 1. Prototype Flow per Frontgrade Manufacturing Flows Document. Devices are tested at 25°C only. Radiation is neither tested nor guaranteed.

- 2. HiRel Flow per Frontgrade Manufacturing Flows Document. Radiation is neither tested nor guaranteed.

- 3. Ceramic Ball Grid Array (CBGA) package option is for Prototype Flow Only.

| Package Option | Associated Lead Finish |

|----------------|------------------------|

| (Z) 400-CLGA   | (C) Gold               |

| (S) 400-CCGA   | (A) Hot Solder Dipped  |

| (C) 400-CBGA   | (A) Hot Solder Dipped  |

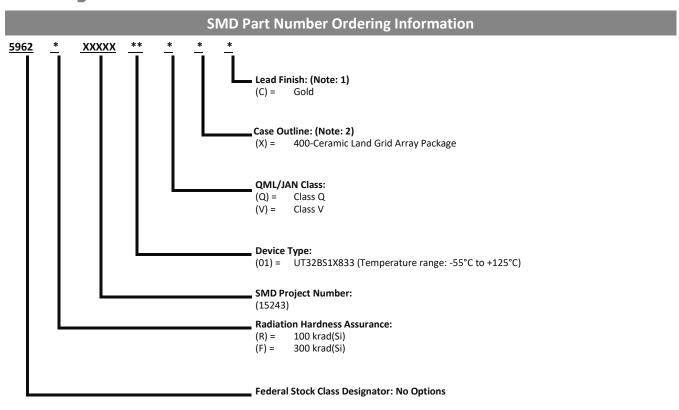

# **Ordering Information**

- 1. Lead finish is "C" (gold) only.

- 2. Frontgrade offers Column Attachment as an additional service for the Ceramic Land Grid Array (Case outline "Y"). If needed, please ask for COLUMN ATTACHMENT when submitting your request for quotation.

# **Revision History**

| Date  | Revision # | Author | Change Description                                                                        | Page #  |

|-------|------------|--------|-------------------------------------------------------------------------------------------|---------|

| 11-14 | -          | ВМ     | Initial release of preliminary datasheet                                                  | All     |

| 01-18 | -          | вм     | Page 01 added SMD number<br>Page 17 added SMD number and QML V                            | 01, 17  |

| 04-18 | -          | BM     | Page 16 - added Screening note 3.                                                         | 16      |

| 06-18 | -          | вм     | Page 16 - Correction to Screening Level Indicator                                         | 16      |

| 10-18 | -          | ВМ     | Page 12 - Parametric Measurement Information - Added Figure 5                             | 12      |

| 08-21 | -          | ВМ     | Page 07 – Updated input tR, tF parameters in ROC Table                                    | 07      |

| 11-23 | 2.0        | ВМ     | Update datasheet to Frontgrade format Page 06 – Channel Pins Table Correction: 25B6 = N17 | All, 06 |

## **Datasheet Definitions**

|                       | Definition                                                                                                                                                                                                                                                                                                     |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Advanced Datasheet    | Frontgrade reserves the right to make changes to any products and services described herein at any time without notice. The product is still in the development stage and the <b>datasheet is subject to change</b> .  Specifications can be <b>TBD</b> and the part package and pinout are <b>not final</b> . |

| Preliminary Datasheet | Frontgrade reserves the right to make changes to any products and services described herein at any time without notice. The product is in the characterization stage and prototypes are available.                                                                                                             |

| Datasheet             | Product is in production and any changes to the product and services described herein will follow a formal customer notification process for form, fit or function changes.                                                                                                                                    |

Frontgrade Technologies Proprietary Information Frontgrade Technologies (Frontgrade or Company) reserves the right to make changes to any products and services described herein at any time without notice. Consult a Frontgrade sales representative to verify that the information contained herein is current before using the product described herein. Frontgrade does not assume any responsibility or liability arising out of the application or use of any product or service described herein, except as expressly agreed to in writing by the Company; nor does the purchase, lease, or use of a product or service convey a license to any patents rights, copyrights, trademark rights, or any other intellectual property rights of the Company or any third party.