# FRONTGRADE

# **APPLICATION NOTE**

**UT700**

**Enable the Ethernet MAC Controller Module**

1/12/2017 Version #: 1.0.1

#### **Table 1: Cross Reference of Applicable Products**

| Product<br>Name | Manufacturer Part<br>Number | SMD#       | Device Type                    | Internal Pic<br>Number |

|-----------------|-----------------------------|------------|--------------------------------|------------------------|

| UT700 LEON      | UT700                       | 5962-13238 | Ethernet MAC Controller Module | WQ03                   |

#### 1.0 Overview

The UT700 LEON 3FT SPARC Processor provides one Ethernet Media Access Controller (MAC) that interfaces between the UT700 LEON'S AMBA AHB and an external Ethernet PHY to an Ethernet network. This Ethernet MAC supports 10/100 Mbits speed in both full- and half-duplex modes. DMA engines are part of the Ethernet MAC design that speeds up the data transaction from the main memory to and from the transmitter and receiver FIFOs'.

Although the Ethernet MAC also provides an additional feature such as the Ethernet Debug Communication Link (EDCL), this feature will not be discussed in this application note. Instead, this application note will focus on how to enable the Ethernet MAC module to communicate with the Ethernet network.

In addition to the Ethernet MAC, this application note will briefly discuss the Ethernet PHY loopback feature for its use in data transaction testing from main memory to the transmitter, through the loopback path to the receiver, and back to the main memory.

This is software centric Application Note, the discussion of hardware in this application note will be restricted to connectivity verification and testing.

Note: Ethernet Interface operation is intended for terrestrial use only, and not guaranteed in radiation environments.

The description in this application note describes how to directly use the memory mapped interface of a specific hardware peripheral. If you are using an operating system such as RTEMS, Linux, and VxWorks or an environment such as BCC then it is recommended to use the infrastructure provided by those environments instead of accessing the peripheral directly as described in this application note.

#### 1.1 Application Note Layout

This application note (AN) starts by providing a brief description of the Ethernet Media-Independent Interface (MII) and its functional purposes. The description of the MII falls under the Ethernet Hardware sections.

After the Ethernet Hardware sections, this AN provides high-level flow diagrams to depict the correct sequential steps to initialize the MAC's transmitter and receiver for data transaction with the Ethernet network. The next section provides the significant order of the enabling of the internal Ethernet blocks. This flow diagram and its elaborations fall under the Ethernet Enable Flow Diagrams.

Finally, we can apply this knowledge using C programming code to enable the UT700 LEON to communicate with the Ethernet network. The programming of C code falls under the Ethernet Programming sections.

These sub-sections are described in detail below:

- Ethernet Hardware

- Ethernet Initialization Flow Diagram

- · Ethernet Programming

#### 2.0 Ethernet Hardware

Since this is a software centric AN, the discussion of hardware will be restricted to connectivity verification and testing.

#### 2.1 Ethernet Media-Independent Interface (MII)

The UT700 LEON Ethernet MAC provides an MII interface to connect to external Ethernet PHYs. This MII interface consists of a Management Data Input/Output (MDIO) interface, transmission, reception, clock and control signals.

The MDIO interface provides a conduit to initialize and program the external Ethernet PHY. The Ethernet PHY provides the output clock signals (TX\_CLK and RX\_CLK) to synchronize the data flow between the Ethernet MAC and the PHY.

The input clock frequency to the Ethernet PHY's depends on its mode of operation. When the Ethernet PHY is operating in MII or RMII mode, the input clocks frequency to the PHY must be set to 25MHz and 50MHz respectively. Since the UT700 LEON Ethernet MAC only supports MII mode operation, a 25MHz input clock frequency will suffice.

The UT700 LEON Functional Manual, **Chapter 14**, provides more information about the Ethernet MAC. Also, see **Figure 14.1** of the UT700 LEON Functional Manual that depicts the Ethernet MAC block diagram and its internal structure.

#### 2.2 Ethernet PHY Loopback Feature

Most Ethernet PHY provides a hardware loopback path that allows data testing without being physically connected to a network. On the other hand, the UT700 LEON Ethernet MAC does not provide any loopback path for testing; if this is a method required for your testing, then software is needed to move data from the receiver's FIFO to the transmitter's FIFO.

# 3.0 Ethernet Initialization Flow Diagram

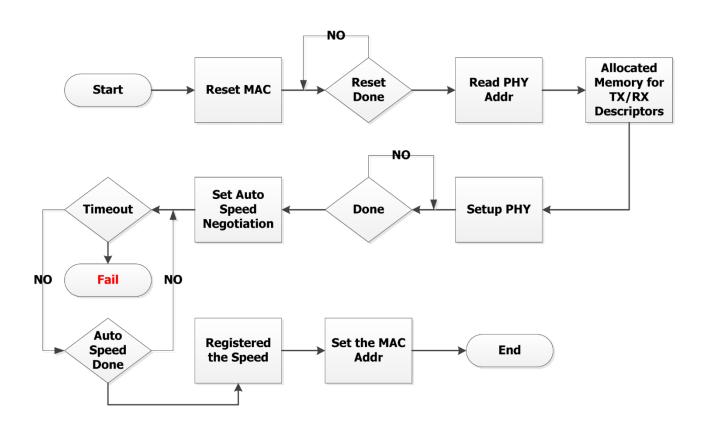

In this section, we will provide a flow diagram that depicts the proper sequential steps to initialize the Ethernet MAC as shown in **Figure 1.**

The initialization process involves both allocating resources from the main memory and the settings of the MAC internal registers. In the following sections, we will provide a basic understanding of the initialization of the individual block as shown in **Figure 1.**

Figure 1: Ethernet Initialization Flow Diagram

#### 3.1 Reset MAC

The reset step allows the MAC's registers to restore to its factory reset state. In this state, it assures the MAC is disabled. Once in this state, we can proceed to initialize the MAC.

#### 3.2 Read PHY Address

The UT700 LEON Ethernet MAC supports multiple Ethernet PHYs, but this example we are only using one PHY. The "Read PHY address" step allows us to send the PHY configuration to the correct PHY.

#### 3.3 Allocate Memory for Descriptors

The UT700 LEON Ethernet MAC includes a DMA engine that supports data packets transfer from the main memory to and from the transmitter and receiver FIFOs. This method of transferring packets improves the throughput of the application by eliminating the software overhead and spinwait time lost for waiting to read or write the FIFOs.

In order to support this feature, additional data structures and data packets buffers are created in the main memory. The data structures are the Ethernet transmitter and receiver descriptors that provide information to the DMA engine on how to move data packets to and from main memory and the FIFOs.

The MAC also provides a simple round robin method to track both the transmitted and received packets using the transmitter and receiver descriptor pointer registers. These registers will increase by one if their respective operation is executed (transmit or receive a packet). These registers are 7-bits wide and upon reaching 0x7F, a subsequent DMA operation will set these registers to 0x00.

These 7-bits registers format can pose an issue on memory scarcity system. If every data packet buffer size is set to the MTU (maximum transfer unit) size, then the memory requirement for this scheme is as follows:

Destination MAC address = 6 bytes

Source MAC address = 6 bytes

Data Size = 2 bytes

Descriptor (word 0/1) = 4 bytes each

Memory Size = (MTU + Descriptors + 6 + 6 + 2) \* 2 \* 128

Memory Size = (1500 + 8 +14) \* 2 \* 128 = 389,632 bytes

Although this simple round robin method does pose an issue of consuming a lot of memory, we can use software to mitigate the memory consumption by using the descriptor WR (Wrap enable) bit to reduce the memory usage.

In this example, we are limiting our memory usage to four set of buffers. We can redirect the descriptor pointer to wrap back to the first buffer when it reaches the fourth buffer using the following method. When a transaction happens on the third transmission, write descriptor with the WR bit set (see section **3.12**). This method will set the descriptor pointer to zero after the fourth buffer is transmitted.

#### 3.4 Speed Negotiation

Many PHYs provide an auto-negotiation mode feature. The PHY on our board has this feature; therefore, we are using this feature to negotiate a connection on our behalf as either, a 10Mbits or 100Mbits link.

#### 3.5 Set MAC Address

Ethernet connections communicate with one another using the MAC address; without it, the Ethernet is inoperable. A wrong perception to the MAC address is the use of an Internet Protocol (IP) address to supersede the MAC address. An IP address is a data link layer address whereas the Ethernet MAC address is a Physical layer address. With this clarification and the setting of the MAC address, we complete the initialization of the Ethernet MAC.

#### 3.6 Ethernet Programming

We learned from the Ethernet Hardware section how the PHY and the MAC are connected and what roles the signals connecting the PHY and the MAC play. We also learned from the Ethernet Initialization section how to initialize the MAC and PHY.

In the following sections, we will provide programming examples to enable the Ethernet module in the UT700 LEON processor. The programming examples are as follows:

- · Reset the Ethernet MAC

- · Read PHY Address

- · Allocate Memory for Descriptors

- Setup PHY, Auto Speed Negotiation

- Setup MAC address

- Transmit and receive data

**Appendix A** shows all the Ethernet MAC Controller registers used in this AN.

#### 3.7 Reset the Ethernet MAC

Resetting of the Ethernet MAC is done by asserting the RS bit in the Ethernet Control Register; see Figure 14.6 of the UT700 Functional Manual. When the MAC reset is completed, RS is de-asserted by the MAC controller.

This step is essential because it disables the MAC and set all the MAC's registers to the factory default.

```

GRETH.ETHCTR.B.RS = 1; // reset the Ethernet MAC

```

#### 3.8 Read PHY Address

Since the UT700 does not have a build-in PHY, users are advised to refer to the PHY reference manual for correct programming.

After the MAC Controller is reset, read the ETHMDC, Ethernet MDIO Control and Status Register for the PHY address; see **Figure 14.10** of the UT700 Functional Manual.

#### 3.9 Allocate Memory for Descriptors

The GRETH's MAC supports DMA's transactions, which provides fast data transfer between main memory and FIFOs'. The byproduct of this DMA scheme is that all the allocated buffers must be word-aligned.

For this example, we used the "almalloc" function to allocate word-aligned buffers. Also, refer to sections **14.2.5** and **14.2.10** of the UT700 Functional Manual for the correct descriptor structure.

#### 3.10 Setup PHY, Auto Speed Negotiation

The PHY we used in this experiment provides an easy way to set the PHY into auto-speed negotiation by resetting the PHY. Users of this AN are advised to refer to the PHY's reference manual for the correct PHY programming sequence.

#### 3.11 Setup MAC Address

The MAC's address is a six bytes long address. Appended code shows how to program the MAC's address in the Ethernet MAC's Address MSB and LSB registers.

```

GRETH.MACMSB.R = 0 \times 00001122; // the upper 16 bits are not used GRETH.MACLSB.R = 0 \times 33445566;

```

#### 3.12 Transmit and Receive Data

Appended are software examples how to transmit and receive an Ethernet data packet from and to the main memory and MAC's FIFOs respectively.

```

#define GRETH BD EN

0x800

#define GRETH BD WR

0x1000

#define GRETH_TXEN

0x1

#define GRETH RXEN

0x2

// Transmit

// TX buffer

Txd.addr = (uint32 t) &tbuf;

Txd.ctrl = GRETH BD EN | size;

// set descriptor enable and buf size

GRETH. ETHCTR.R = GRETH. ETHCTR.R | GRETH_TXEN;

// Receive

Rxd.addr = (uint32 t) & rbuf;

// RX buffer

Rxd.ctrl = GRETH BD EN | size;

// set descriptor enable and buf size

GRETH. ETHCTR.R = GRETH. ETHCTR.R | GRETH RXEN;

```

Note: Transfer buffer THEN reset the descriptor pointer to zero

```

Txd.ctrl = GRETH_BD_EN | GRETH_BD_WR | size;

```

The device MAC address and the Ethernet frame are required for Ethernet communication. The Ethernet frame is beyond the scope of this AN. Nonetheless, to make this experiment successful, the first 12 bytes of the buffer must contain the destination and source address and the subsequent two bytes contain the size of the data.

## 4.0 Summary and Conclusion

After going through this AN, the reader should know how to enable the Ethernet MAC Controller and how the descriptors are setup to support DMA transactions between the main memory and the MAC's FIFOs. The reader should also take note that this Ethernet MAC Controller does not support any CRC generation required by any data link layer transport protocol.

For more information about our UT700 LEON 3FT/SPARC™ V8 Microprocessor and other products please visit our website, <a href="https://frontgrade.com/contact-us">www.frontgrade.com/contact-us</a>.

### **Appendix A**

The header files are designed for this application note purpose only.

```

/**************************

* MODULE: Ethernet Media Access Controller (MAC)

#define GRETH ADDR 0x80000E00

struct GRETH _TAG {

union {

vuint32 t R;

// Figure 14.6: Ethernet Control

Register

struct {

vuint32_t ED :1;

vuint32_t BS :3;

// EDCL Available

// EDCL Buffer Size

vuint32_t RES27to08 :20; //

} B;

} ETHCTR;

union {

vuint32 t R;// Figure 14.7: GRETH Status and Interrupt Source Register

struct {

vuint32_t RES31to08 :24;  //

} B;

} ETHSIS;

union {

vuint32 t R;// Figure 14.8: Ethernet MAC Address MSB

struct {

vuint32 t RES31to16 :16;

vuint32 t ADDR MSB :16;

// MAC MSB address

} MACMSB;

union {

vuint32 t R;// Figure 14.9: Ethernet MAC Address LSB

struct {

vuint32 t ADDR LSB :32;  // MAC LSB addres

```

```

} MACLSB;

union {

vuint32 t R;// Figure 14.10: Ethernet MDIO Control and Status Register

vuint32_t PHY_ADDR :5;  // Rx or Tx Data

vuint32_t REG_ADDR :1;  // address of the PHY

vuint32_t RFS5 ·1

struct {

// address of the register

// Not Valid

vuint32 t NV :1;

vuint32 t BU :1;

// Busy

// Link Fail

vuint32 t LF :1;

// Read

vuint32_t RD :1;

vuint32 t WR :1;

// Write

} B;

} ETHMDC:

union {

vuint32 t R;// Figure 14.11: Ethernet Transmitter Descriptor Pointer

Register

struct {

vuint32_t TXDTRA :22;  // Transmitter Descriptor Table addr

vuint32_t TX_DESC :7;  // descriptor incremental field

vuint32 t RES2to0 :3;

//

} B;

} ETHTDP;

union {

vuint32 t R; // Figure 14.12: Ethernet Receiver Descriptor Pointer

Register

struct {

vuint32_t RXDTRA :22;  // Receiver Descriptor Table addr

vuint32 t R`X DESC :7;  // descriptor incremental field

vuint32 t RES2to0 :3;

//

} B;

} ETHRDP;

};

```

# **Revision History**

| Date       | Revision # | Author | Change Description | Page # |

|------------|------------|--------|--------------------|--------|

| 11/07/2016 | 1.0.0      | MTS    | Initial Release    |        |

| 1/12/2017  | 1.0.1      | MTS    | Added a note       | 1      |

|            |            |        |                    |        |

|            |            |        |                    |        |

Frontgrade Technologies Proprietary Information Frontgrade Technologies (Frontgrade or Company) reserves the right to make changes to any products and services described herein at any time without notice. Consult a Frontgrade sales representative to verify that the information contained herein is current before using the product described herein. Frontgrade does not assume any responsibility or liability arising out of the application or use of any product or service described herein, except as expressly agreed to in writing by the Company; nor does the purchase, lease, or use of a product or service convey a license to any patents, rights, copyrights, trademark rights, or any other intellectual property rights of the Company or any third party.